Sistemas HVDC

SESIÓN 2 : Operación e impacto de Sistemas HVDC en redes existentes

Junio 10

## Issues derived from the Multiplicity of new HVDC Links Embedded to AC Transmission Grids Experience in Brasil

MARCIO SZECHTMAN President - Technical Council CIGRE Eletrobras Chief Transmisson Officer

**CONVERSATORIO:**

## Philosophy for Implementing new HVDC Schemes in Brazil

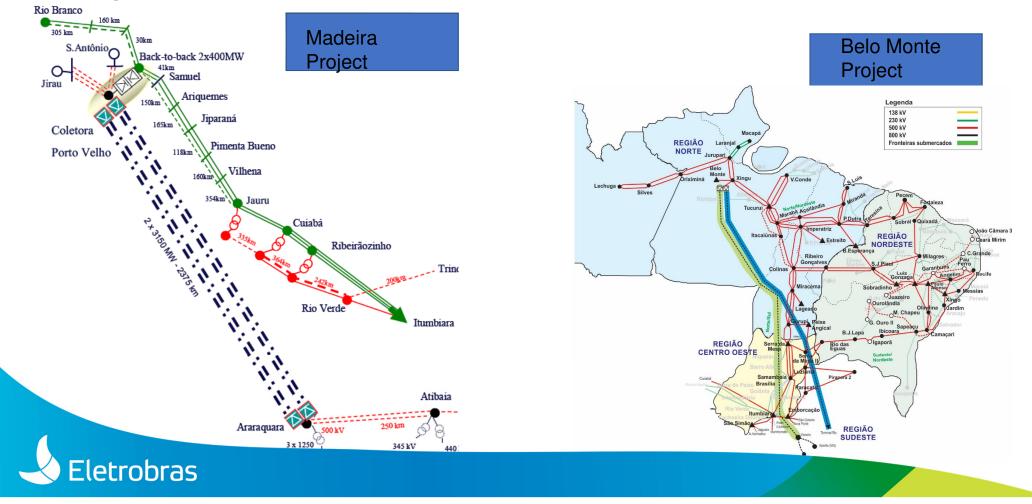

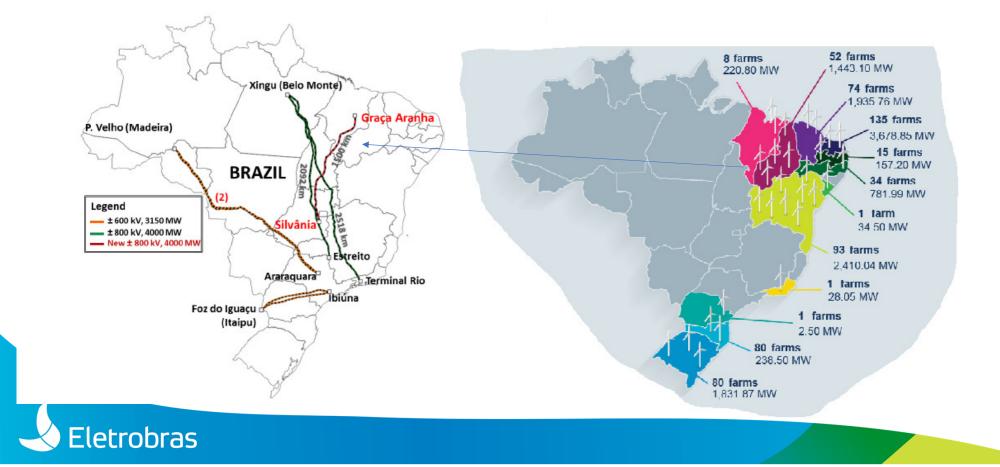

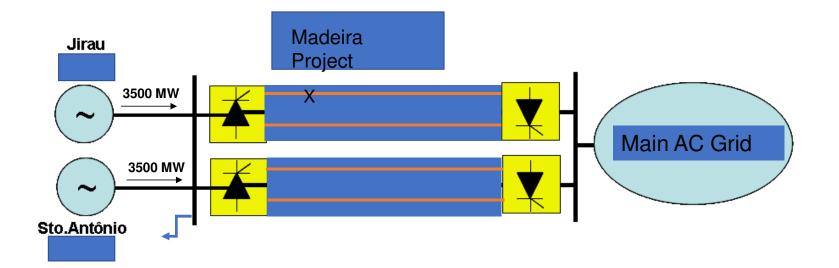

- ✓ Differently from China, Brazil has been planning the HVDC links in a pair of Bipoles

- ✓ Two standards in the country:

- ✓ ± 600 kV 3,150 MW 2,625 A; Itaipu and Madeira Bipoles

- ✓ ± 800 kV 4,000 MW 2,500 A: Belo Monte Bipoles

- ✓ In parallel, they can transmit, respectively:

- ✓ 6300 MW

- ✓ 8000 MW

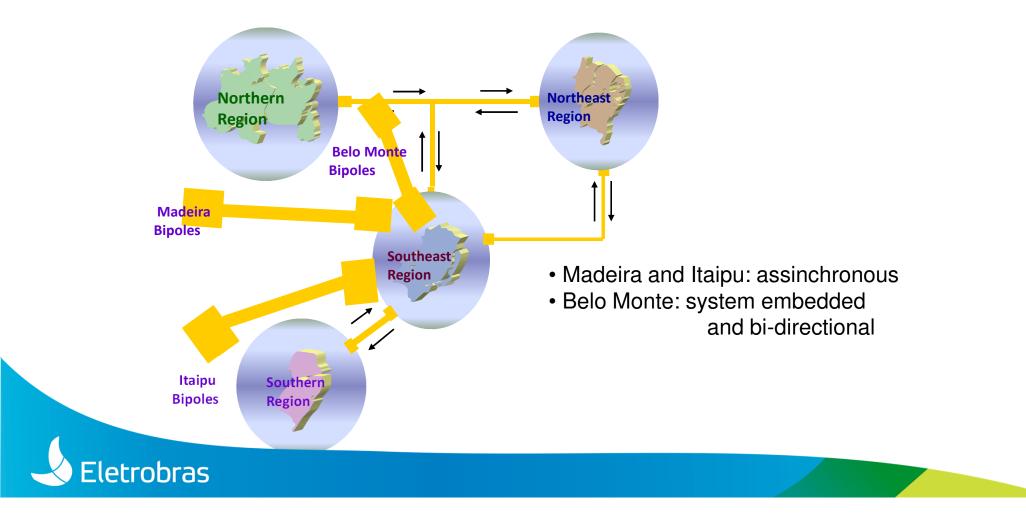

- ✓ Itaipu and Madeira links: were designed to allow bipolar parallel operation

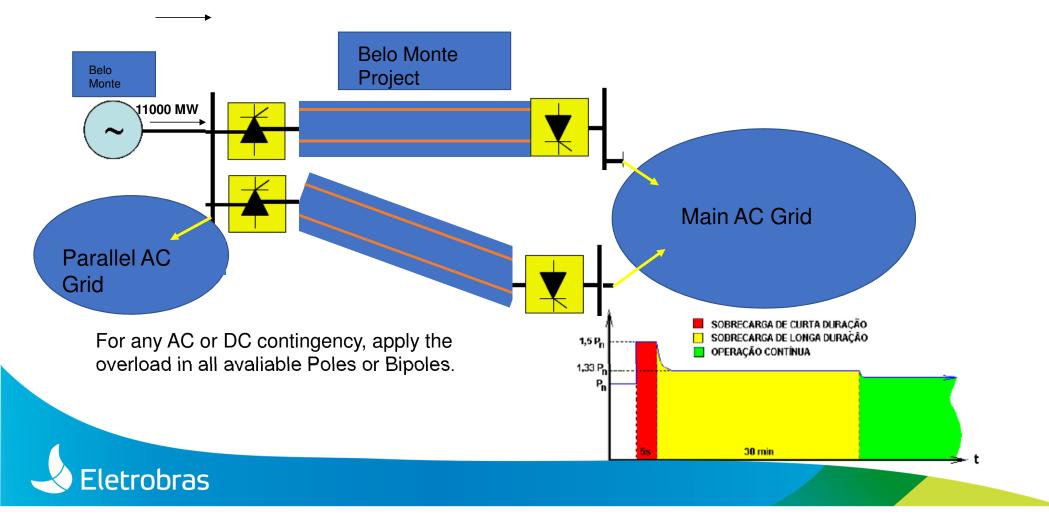

- ✓ Belo Monte links: the receiving end terminal selected differently for each Bipole: greater concern of loosing the entire two Bipoles for an AC fault at the receiving end terminal

#### Philosophy for Implementing new HVDC Schemes in Brasil

- ✓ Differently from China, Brazil has been planning the HVDC links in a pair of Bipoles

- ✓ Two standards in the country:

- ✓ ± 600 kV 3,150 MW 2,625 A; Itaipu and Madeira Bipoles

- ✓ ± 800 kV 4,000 MW 2,500 A: Belo Monte Bipoles

- ✓ In parallel, they can transmit, respectively:

- ✓ 6300 MW

- ✓ 8000 MW

- ✓ Itaipu and Madeira links: were designed to allow bipolar parallel operation

- ✓ Belo Monte links: the receiving end terminal selected differently for each Bipole: greater

concern of loosing the entire two Bipoles for an AC fault at the receiving end terminal

#### VSC x LCC: Recovery from a DC line fault

Fault current cleared by AC breaker (3 cycles); full recovery time, from 700 to 1500 ms; with DC breakers or full bridge, time will be less

Fault current cleared by Thyristor control in 10 ms; typical straight forward recovery time in the range of 400 ms, including arc deionization

HVDC response due to a mid-line pole DC fault: left VSC System; right typical LCC Scheme

## **Configurations of Madeira and Belo Monte HVDC** Projects

## **Need for a further HVDc link to power flow control in** avery meshed network

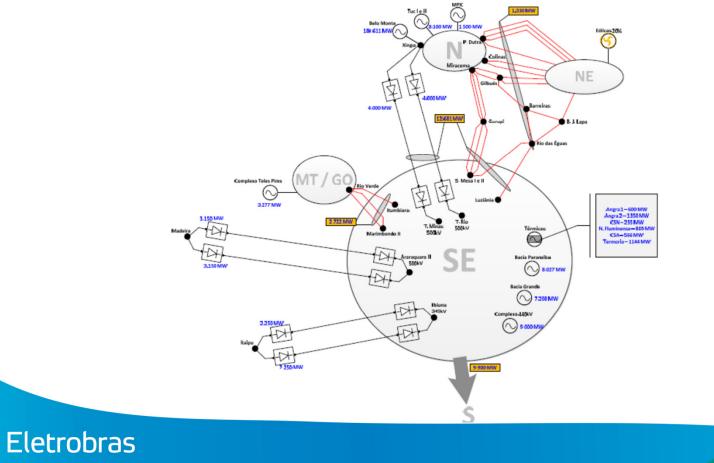

**Therefore after completion of the Madeira and Belo** Monte projects, we will have 4 PoC in the Southeast region (SE) where major load is placed.

#### **System Effect of HVDC Links**

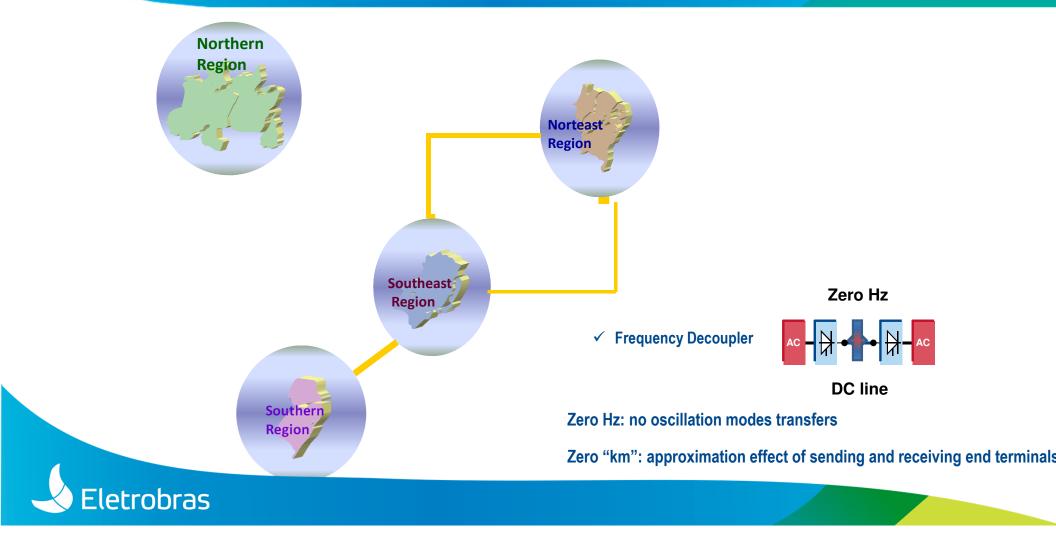

## The Benefit of close integration of regions

# **Overload Cycles Specified**

For a pole outage, apply the overload in the other 3 Poles, so as to keep the same Pdc level.

Eletrobras

# **Overload Cycles Specified**

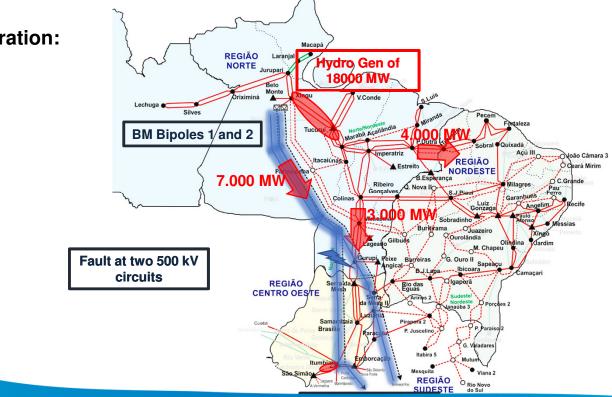

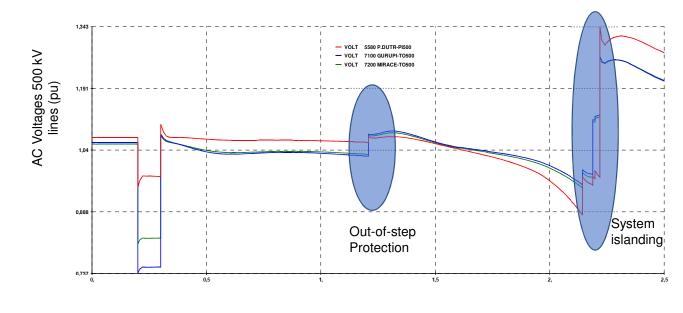

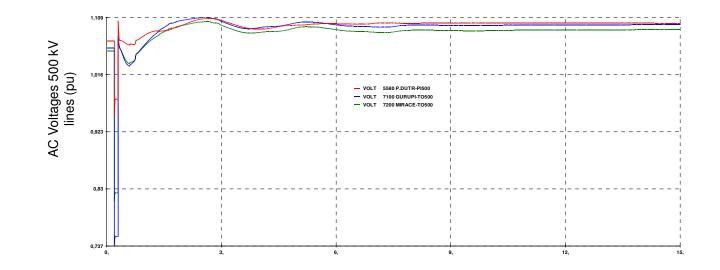

## **Stability Studies Results (Belo Monte)**

Main Configuration:

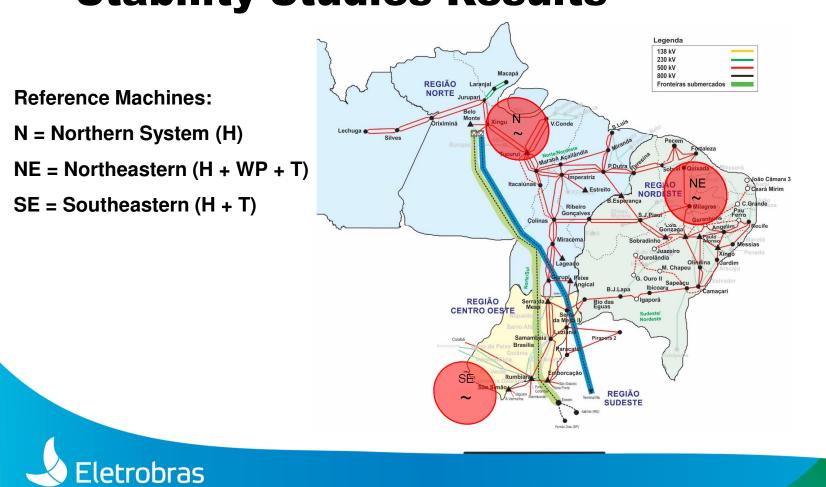

## **Stability Studies Results**

# **Results with no overload**

# **Results with no overload**

Time (s)

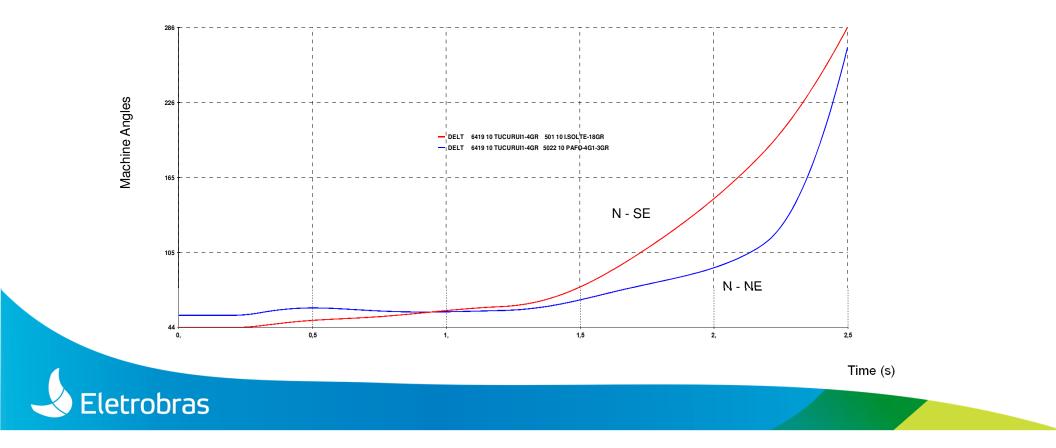

## **Results with no overload - worst**

Machine Angles

Time (s)

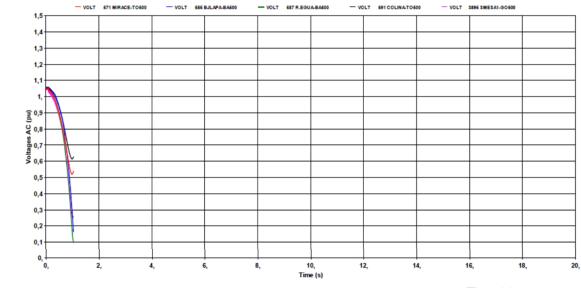

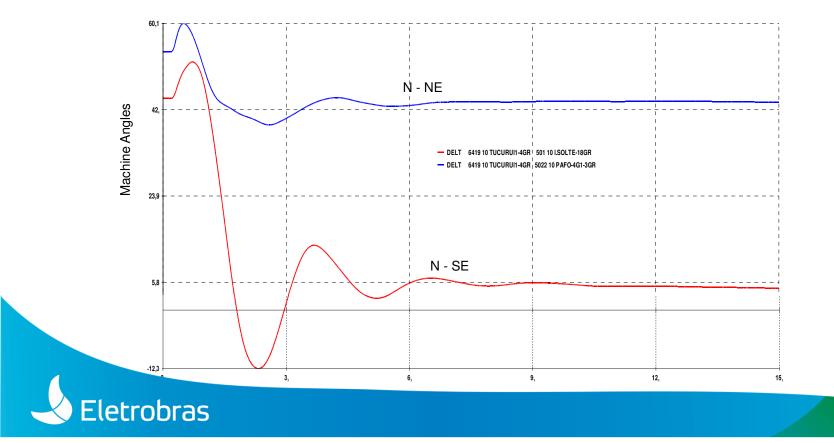

# **Results with 33% overload**

# **Results with 33% overload**

Time (s)

## Conclusions

- 1. HVDC links cannot longer be considered as separate "entities" in the Grid.

- 2. Coordination studies to assess the external signals (from the AC system) that may require run-up or run-down of the HVDC dispatch, are becoming of greater importance.

- 3. HVDC overload requirements have to be carefully analyzed.

- 4. HVDC embedded in the AC Grid may provide fundamental contributions to system stability and security.

- 5. Current studies contemplate: key external signals to be considered by the Master Control; flexibility in the overload level and ramp time to be set.

- 6. Objective is to minimize the number of Hydro machines to be dropped to maintain system stability.

# Muchas Gracias!!

## Gracias